Le 3 et 2 nm pour bientôt certes, mais sous quelle forme ? |

————— 25 Janvier 2021 à 15h59 —— 13000 vues

Le 3 et 2 nm pour bientôt certes, mais sous quelle forme ? |

————— 25 Janvier 2021 à 15h59 —— 13000 vues

Ces derniers temps, chaque région géographique commence à annoncer la prise en charge de projets portant sur la production de puces de nouvelle génération, notamment en 3 nm chez les Américains - en partenariat avec Samsung - ou en 2 nm chez les Européens, et probablement que d'autres annonceront d'ici peu leurs ambitions à ce sujet. Voir un tel engouement de la part des États envers l'industrie électronique peut être signe de l'importance accordée à ce domaine ou des besoins d'indépendance vis-à-vis de certains acteurs sur le marché, toutefois ce ne sera pas le débat du jour. En effet, il est nécessaire tout d'abord de rappeler que si de loin cela semble juste à la classique course du kikimètre à celui qui a la plus petite - taille de gravure bien entendu -, il faut se souvenir que derrière, cela demande pas mal d'évolutions techniques avant de voir des productions de masse du 3 et 2 nm.

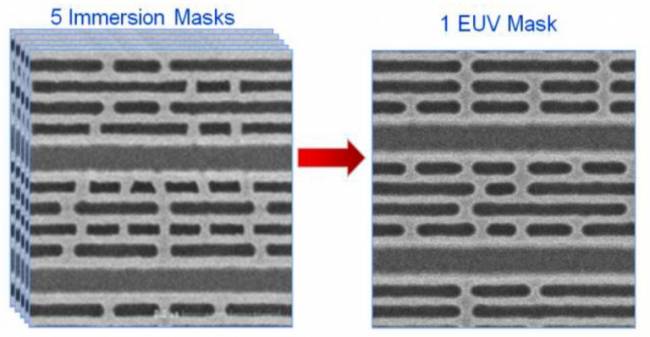

Le passage à la gravure par ultraviolet, appelé EUV, est un acteur essentiel à la miniaturisation des puces. Déjà employé pour les puces en 5 nm, celui-ci permet notamment d'améliorer le rendement et la qualité grâce à une optimisation du nombre de masques nécessaire, donnant des galettes mieux gravées et plus fidèles aux prévisions. Cependant, la technologie n'en est qu'à ses débuts, et les machines ne sont pas encore majoritaires dans les usines du domaine, avec des outils de développement qui sont encore en phase préliminaire pour le routage des puces.

Il y a donc fort à parier que dans un premier temps, les futurs nodes seront - tout comme aujourd'hui - utilisés d'abord pour des petits dies ou des circuits spécialisés, limitant leur utilisation dans l'industrie de l'ordinateur et des composants hardware. Il est fort probable qu'à l'instar du 7 nm, le 5 nm soit majoritairement utilisé durant les 3 prochaines années dans notre secteur, le temps d'obtenir suffisamment de machine en EUV et de rendement optimal sur des grands dies.

Il s'agit là d'une des avancées majeures pour le passage au 3 nm et plus encore : revoir la construction des transistors et pouvoir remplacer l'actuel FinFET. Celui-ci commence à avoir un peu d'âge, et son architecture n'est pas la plus efficace sur les gravures en dessous des 3 nm, la construction de la source verticale devenant plus compliquée. Afin de pallier à ce problème, une nouvelle structure est proposée : les transistors nanowire et nanosheet, et plus précisément le GAAFET, qui est largement mis en avant actuellement par Samsung ou par Intel, qui en fait son poulain pour le 3 nm.

La technologie permet de transformer le canal en une multitude de couches plus ou moins larges de semiconducteur, en laissant la grille complètement entourer ce canal, augmentant de ce fait les jonctions entre les deux électrodes du transistor tout en réduisant la taille du canal. Les avantages majeurs seraient une plus grande fiabilité sur les gravures les plus fines et une tension de seuil plus faible, atteignant les 0,3 V. Nous devrions donc avoir des transistors moins gourmands en énergies, permettant d'optimiser un peu plus les températures, puissances ou fréquences selon les besoins et les goûts.

Du côté européen, c'est la technologie FD-SOI qui fait ses débuts dans le domaine des puces de basse consommation, qui propose tout aussi de belles promesses sur le papier : tension de seuil plus faible que les FinFET, coûts de production plus faible et une fréquence de coupure deux fois plus élevée, de quoi faire rêver. Or, le projet d'une industrie électronique purement basée sur le vieux continent n'en est qu'à ses débuts, il faut voir quels seront les choix tehcnologiques utilisés - le FD-SOI se limitant encore à des tailles de gravures loin des 2 nm - et entre les promesses et la réalisation, il reste du temps et surtout un fossé sur le résultat final, à voir d'ici quelques années le résultat.

Le dernier grand point pour l'évolution de nos puces afin d'obtenir le meilleur lors du passage au 3 et 2 nm sera de revoir les matériaux employés pour la construction des éléments électroniques. Actuellement, le silicium domine pour les semiconducteurs, mais la forme employée actuellement n'est pas la plus efficace en matière de consommation électrique ou de rapidité de commutation. En passant à une technologie de matériaux dits à haute mobilité - ou HMC, pour High Mobility Channel - pour la construction de certaines électrodes, il reste possible d'augmenter les fréquences de fonctionnement des puces tout en abaissant la tension de seuil.

Comparaison des courants admissibles entre un canal en silicium pur et en un autre en HMC.

Renforcée par les améliorations que proposent les transistors en nanosheet, nanowire ou FD-SOI, ce changement de matériau permettrait d'obtenir de vraies améliorations - et un fossé considérable - vis-à-vis des générations précédentes de puces. Restons tout de même sur nos gardes à l'heure actuelle : pour l'instant, seuls des procédés en prototype sont réalisés, et il n'est pas impossible que des difficultés se montrent lors des tentatives de productions de masse. De plus, ces évolutions sont surtout plus prioritaires pour le marché de la faible consommation d'énergie et du mobile, comme le montre le dernier contrat entre Apple et TSMC sur le 5 nm. De belles avancées et de belles promesses certes, mais pensez bien à attendre encore quelques années avant de voir ces technologies arriver dans nos cartes graphiques ou CPU, à moins que le marché et la science évoluent d'ici là.

| Un poil avant ?Un boitier-chaussure proposé par la collaboration entre Artifact Studio et NZXT | Un peu plus tard ...Live Twitch • Un chauve à Dubaï (Hitman 3) |  |