TSMC se lasse de jouer des rectangles dans des cercles ; le fondeur veut de nouveaux wafers ! |

————— 21 Juin 2024 à 14h14 —— 35850 vues

TSMC se lasse de jouer des rectangles dans des cercles ; le fondeur veut de nouveaux wafers ! |

————— 21 Juin 2024 à 14h14 —— 35850 vues

La rumeur du jour risque de vous en remémorer une plus ancienne : la Taiwan Semiconductor Manufacturing Company envisagerait de changer de format de wafers ; pas en jouant seulement sur leur taille, mais aussi sur leur forme. Le fondeur souhaiterait en effet passer à des wafers rectangulaires.

WSE Cerebras

Actuellement, les wafers en silicium ont une forme de disques. Ils peuvent avoir différents diamètres. Celui des plus imposants est de 300 mm. Logiquement, prélever des carrés ou des rectangles dans un cercle implique des pertes. De plus, face à une demande croissante, démultipliée par l’engouement autour de l’intelligence artificielle, les capacités de production sont insuffisantes. L’un des leviers étudiés par TSMC pour augmenter ses capacités est le passage à des wafers rectangulaires de 510 x 515 mm. C’est du moins le plan mis sur la table par le Nikkei Asia.

Cette affaire vous en rappelle peut-être une plus ancienne : celle des wafers de 450 mm (mais toujours ronds). Projetés dans les années 2010, nous nous interrogions toujours sur leur absence en 2017. Quelques années plus tard – en 2022 – nous apprenions finalement les tenants et aboutissants de l’avortement de ces wafers de 450 mm, dont l’embryon n’avait pas été initié par des impératifs technologiques, mais plutôt par une démarche conservatrice de maintien d’un leadership. Selon les informations de Nikkei Asia, cette fois, l’innovation serait bien le principal moteur.

Factuellement, par rapport aux wafers circulaires de 300 mm de diamètre, des wafers rectangulaires de 510 x 515 mm offriraient une surface utilisable environ 3,7 fois supérieure. Ils permettraient donc de produire plus de puces par plaquette et de réduire les déchets sur les bords. L’article source explicite : « L'idée derrière cette nouvelle approche est d'utiliser des substrats rectangulaires semblables à des panneaux, plutôt que les wafers ronds conventionnels utilisés aujourd'hui, ce qui permettrait de placer plus de puces sur chaque wafer ».

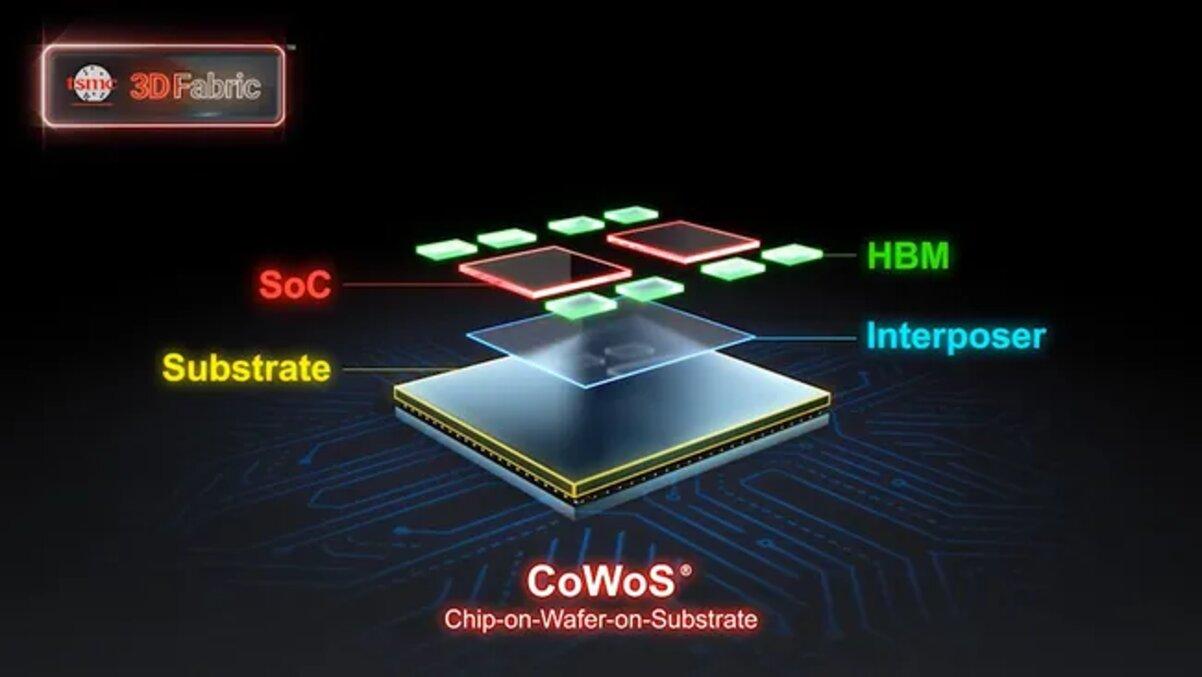

Outre les gains inhérents au changement de forme, de nouveaux substrats d’une plus grande surface s’avéreraient indispensables pour répondre à la complexité des puces de prochaines générations. Les techniques de conditionnement avancées telles que le CoWoS (chip-on-wafer-on-substrate) atteindront leurs limites à mesure que la taille des puces augmentera, que plus de mémoire sera intégrée, etc. Pour illustrer cette tendance, l’article du Nikkei renseigne des estimations faites Morgan Stanley stipulant que seulement 16 puces B200 (Blackwell) peuvent être fabriquées sur un wafer – en supposant que le rendement de production soit de 100 % ; qu’en comparaison, cette quantité est de 29 pour les H200 et H100.

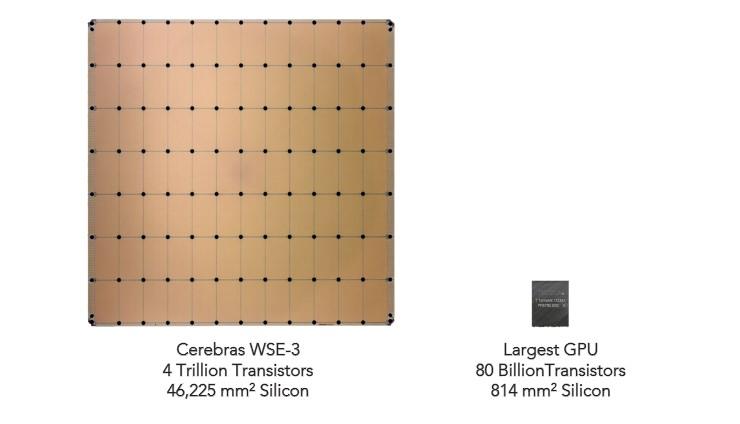

Ajoutons que dans le cas du Cerebras WSE, ce rendement tombe même à un par wafer. Les trois générations Wafer Scale Engine occupent en effet, comme leur nom l'explicite, un wafer entier. Une fois raboté au format carré, celui-ci accouche d'un énorme processeur de 21,5 cm de côté (sur la base d'une aire de 462,25 mm2, bien que √(2) × 150 donne 21,21 pour être précis).

Bien entendu, changer le format des wafers impliquera de changer les outils de fabrication et de production. Toujours selon la source, TSMC collaborerait déjà avec des fournisseurs d’équipements et de matériaux dans ce cadre. Notre confrère précise que ce développement n’en est encore qu’à ses débuts, et que sa concrétisation prendre plusieurs années. C’est un plan à long terme, qui devrait s'étaler sur cinq à dix ans.

Enfin, si vous vous demandez pourquoi les wafers sont ronds, c’est simplement parce qu'ils ont cette forme dès le départ… Vous voilà plus avancés ? Bon, l’un de vous, Feunoir, apportait une réponse plus explicite en commentaire en 2017 dans un des articles susmentionnés. Pour le paraphraser, les lingots de silicium utilisés pour produire la plaquette sont de forme circulaire en raison du processus de fabrication qui consiste à plonger un cristal de semence dans du silicium en fusion, à le faire tourner et à l'extraire progressivement à mesure que le cristal grandit. C’est une méthode appelé procédé de Czochralski.

La mine d'un gros crayon © Wikipedia

| Un poil avant ?Microsoft loue les facultés gaming des PC Arm sous Windows 11 24H2 | Un peu plus tard ...Ryzen AI : des processeurs inédits et un premier test |  |