TSMC fait le point sur ses technologies et leur production |

————— 03 Juin 2021 à 09h45 —— 12753 vues

TSMC fait le point sur ses technologies et leur production |

————— 03 Juin 2021 à 09h45 —— 12753 vues

Il est loin le temps de la discrétion pour TSMC. Pour assurer sa visibilité, mais aussi pour rassurer ses clients, ses investisseurs et les analystes, TSMC fait régulièrement le point sur sa feuille de route et de sa situation. Ce mois-ci, le fondeur taïwanais a profité de son TSMC Technology Symposium pour le faire. D'abord avec une "roadmap" simple et facile à comprendre, résumant ce qui a été réalisé entre 2017 et 2020, qui fut avant tout l'ère de la famille du 7 nm — un succès phénoménal commercial et technique en tout point de vue avec plus d'un milliard de puces fabriquées depuis 2018 — mais aussi le début du 5 nm et de la conception du 3 nm, et pour ces deux derniers ça ne fait encore que commencer.

Tout porte à croire que le 5 nm est parti pour répliquer l'exploit du 7 nm, au fur et à mesure de l'augmentation de la capacité de production et des transitions de la clientèle, et devrait bientôt reprendre la place du node précédent, alors que celui-ci voit sa croissance logiquement ralentir pour atteindre petit à petit le rythme plus calme du procédé 16 nm — la troisième technologie la plus sollicitée chez le fondeur. N'oublions pas que la famille 7 nm inclus également le 6 nm ou N6 et ce dernier aussi gagne de l'importance. En effet, TSMC s'attend déjà à ce qu'il finisse par représenter 48 % de tous les wafers qui sortiront de ses fabs d'ici là fin 2021, alors qu'il n'en était qu'à 15 % fin 2020, ce qui sous-entend naturellement une très forte demande de la part de sa clientèle. Et pourquoi pas pour un refresh de Zen 3 chez AMD, et en 3D ?

Concernant le 5 nm, en production depuis 2020 et dont 500 000 wafers ont déjà été livrés à ce jour (soit approximativement une centaine de millions de puces), l'objectif est de quadrupler la capacité d'ici 2023 par rapport à 2020, naturellement afin de pouvoir soutenir le passage au 5 nm de ses plus gros clients, derrière Apple. Et de ce côté-là, TSMC affirme être très satisfait du déroulement, les rendements du 5 nm étant a priori même meilleurs que le furent ceux du 7 nm lors de même étape. Ceci serait dû à une simplification de la production grâce à la multiplication des couches EUV et de son usage, contrairement au 7 nm qui mélangeait encore DUV et EUV.

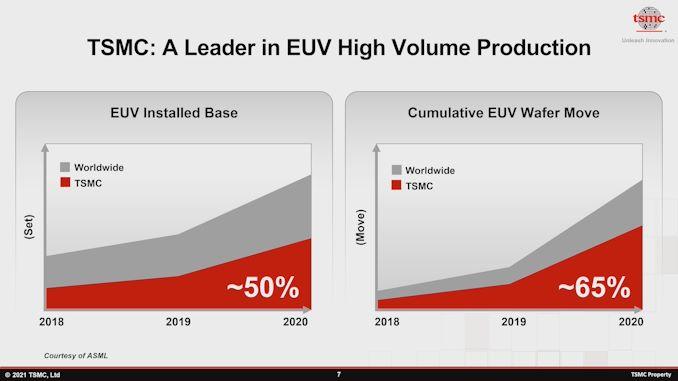

TSMC aime aussi à rappeler qu'il possède environ 50 % du parc de machines lithographiques EUV dans le monde et qu'avec celles-ci il fabrique à ce jour pas moins de 65 % des wafers EUV — clairement, le fondeur est assis sur des bases extrêmement solides, avec un leadership qui ne risque pas d'être remis en question de sitôt. Petite anecdote, alors qu'ASML n'a que récemment annoncé ses pellicules EUV, TSMC affirme avoir utilisé une solution maison dès 2019, qui marche visiblement très bien si l'en on croit les rendements du N5. En sus, le fondeur aurait réussi à considérablement améliorer la durabilité des masques EUV — jusqu'à présent l'une des problématiques majeures avec l'EUV — et espère bien atteindre encore cette année un niveau de réutilisabilité équivalent à un masque DUV.

Le dernier point abordé est celui du 4 nm ou N4, une amélioration mineure du N5 avec une densité supérieure de 6 %, mais qui pourrait endosser le même rôle que s’apprête à jouer le N6 vis-à-vis du N7 et devrait donc intéresser bon nombre de clients de TSMC. La production dite de risque doit démarrer au troisième trimestre. Bref, le fondeur est indéniablement passé maître dans l'art de faire feu de tout bois et rien ne semble pouvoir l’arrêter dans son avancée implacable. Pendant ce temps-là, chez Intel... (Source)

| Un poil avant ?Micron dévoile ses 1ers SSD PCIE 4.0, de la NAND 3D 176L pour le mainstream | Un peu plus tard ...MSi dévoile une carte spéciale pour ses 35 ans |  |