TSMC donne le programme jusqu’au 1,6 nm |

————— 29 Avril 2024 à 17h57 —— 38824 vues

TSMC donne le programme jusqu’au 1,6 nm |

————— 29 Avril 2024 à 17h57 —— 38824 vues

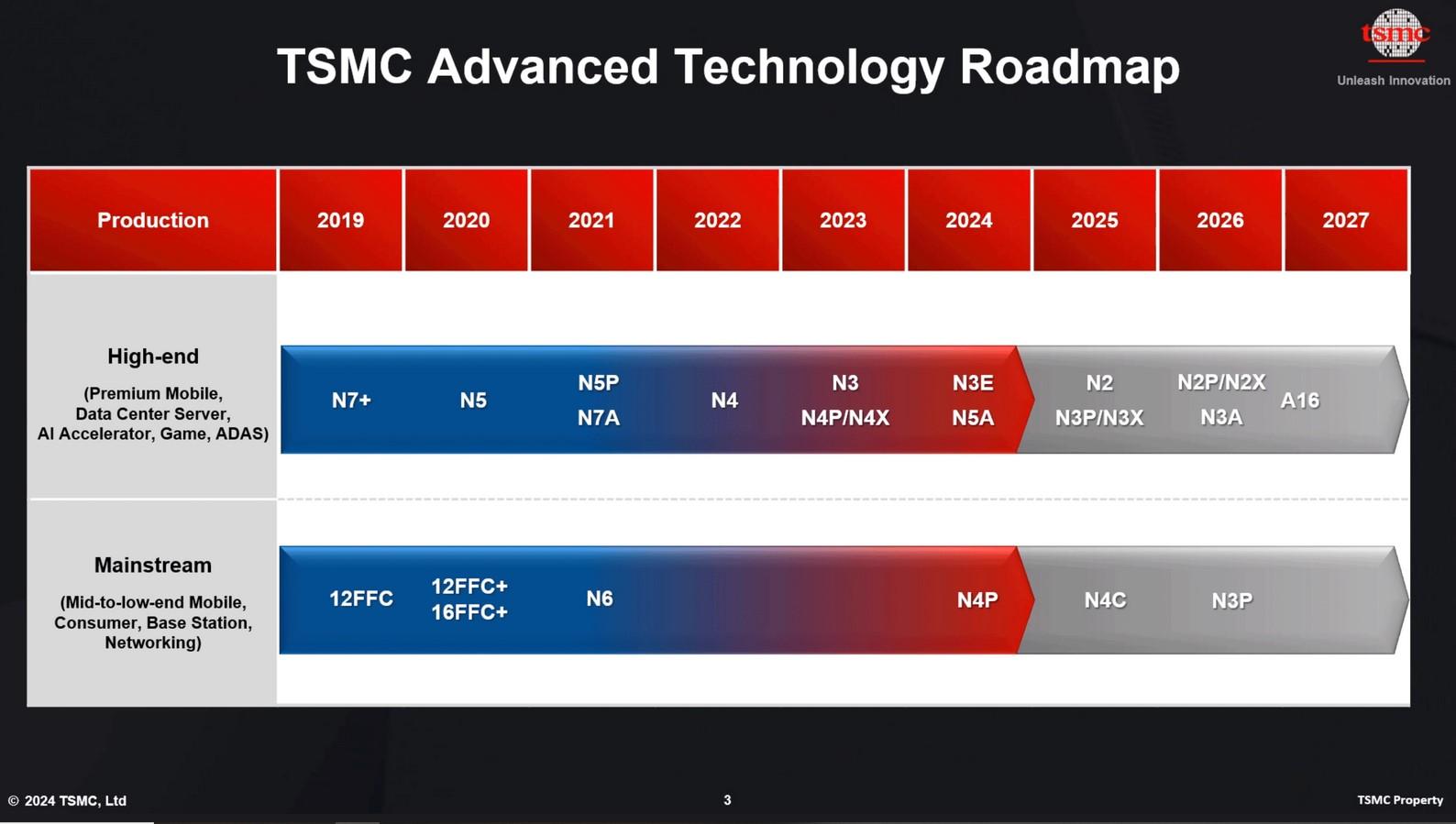

La semaine dernière, dans le cadre de son North American Technology Symposium 2024, le fondeur TSMC (Taiwan Semiconductor Manufacturing Company) a dévoilé sa feuille de route pour ses prochains nœuds de gravure . À l'instar d'Intel, qui a présenté la sienne en février dernier avec l'ambition de reprendre le leadership, l’entreprise fixe le cap jusqu’en 2027, année du déploiement prévisionnel du A16, soit un processus de gravure en 1,6 nm.

Avant de parvenir à une telle finesse, TSMC, qui grave actuellement en 3 nm au mieux, passera par le 2 nm. Comme souvent, le 2 nm impliquera différentes variantes. La première, baptisée N2, doit arriver à son terme l’année prochaine – plus précisément au cours du second semestre 2025. L’année suivante, en 2026, le fondeur introduira les N2P et N2X.

Le programme de TSMC jusqu'à la fin du quinquennat d’Emmanuel Macron © TSMC

Comme prévu, la gravure en 2 nm rimera avec transistors de type nanofeuilles. Comme montré dans l’image ci-dessous, avec ce type de transistors, la grille est en contact avec le canal de tous les côtés – d’où le nom de GAA, gate-all-around. Cet empilement permet aux fabricants de puces d'augmenter la largeur des canaux pour accroître les performances ou de la réduire pour diminuer la consommation d'énergie.

© Semiconductor Engineering

Concrètement, par apport au N3E, le N2 doit accroître la densité de 1,15 fois ; contribuer à réduire la conso d’énergie de 25 à 30 % et à augmenter les perfs de 10 à 15 %. Le N2 sera le nœud standard. Le N2P sera une version optimisée pour le segment grand public, tandis que le N2X doit plutôt cibler le HPC.

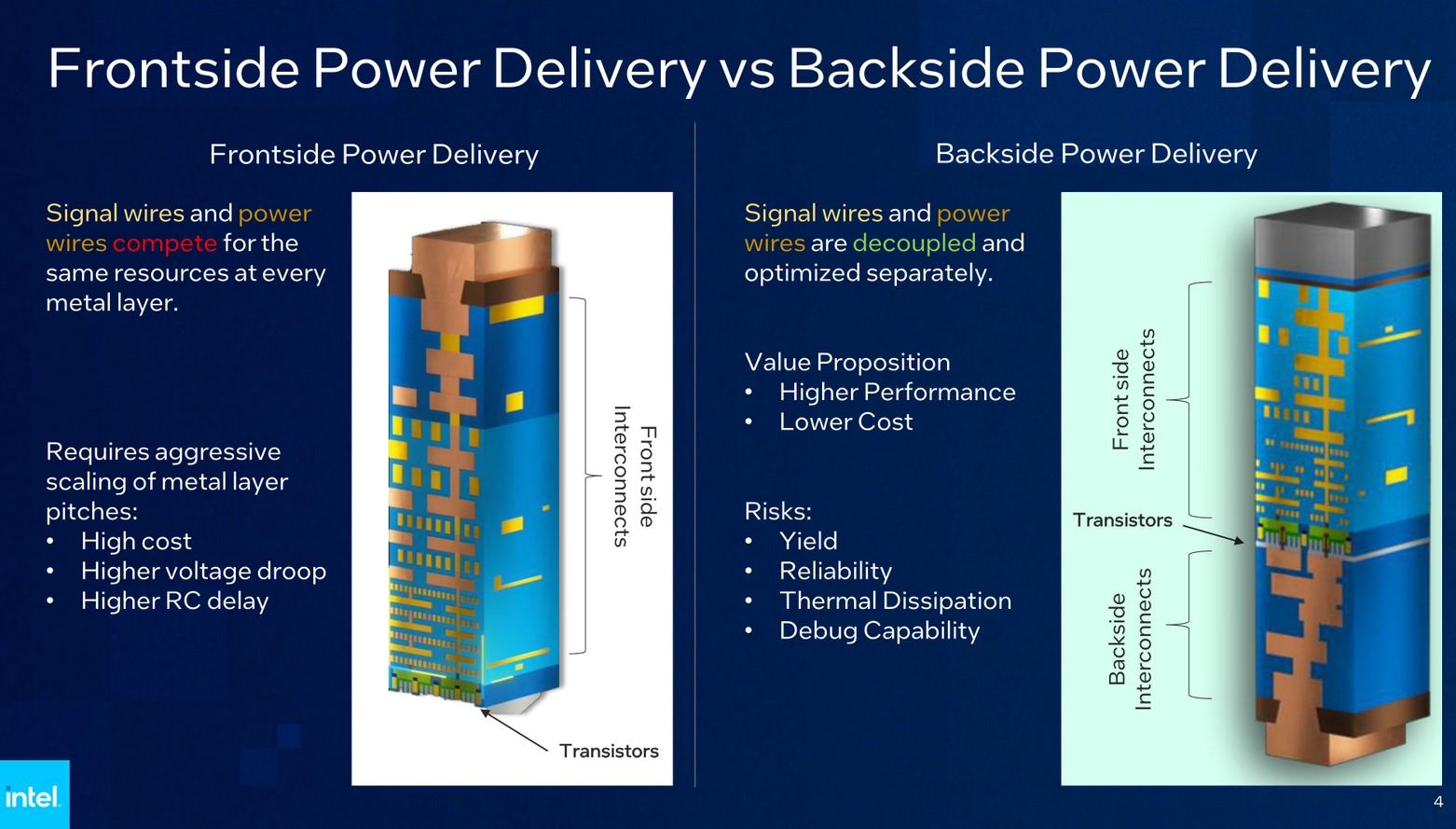

Finalement, le N2 de TSMC n’impliquera pas de distribution d'énergie par la face arrière (backside power delivery en anglais). Chez TSMC, cette technologie n’entrera en jeu qu’à partir du A16 ; le 2 nm va donc conserver des mécanismes de distribution d'énergie plus conventionnels.

Par ailleurs, toujours en matière d’alimentation, le N2 introduira un nouveau condensateur SHPMIM (super-high-performance metal-insulator-metal). Selon TSMC, ce dernier offre une densité de capacité plus de deux fois supérieure à celle du SHDMIM (super-high-density metal-insulator-metal), réduit la résistance de feuille et la résistance de via de 50 % par rapport à son prédécesseur. Bref, ce changement doit contribuer à renforcer la stabilité de l'alimentation électrique, donc in fine, à augmenter les performances et réduire la consommation.

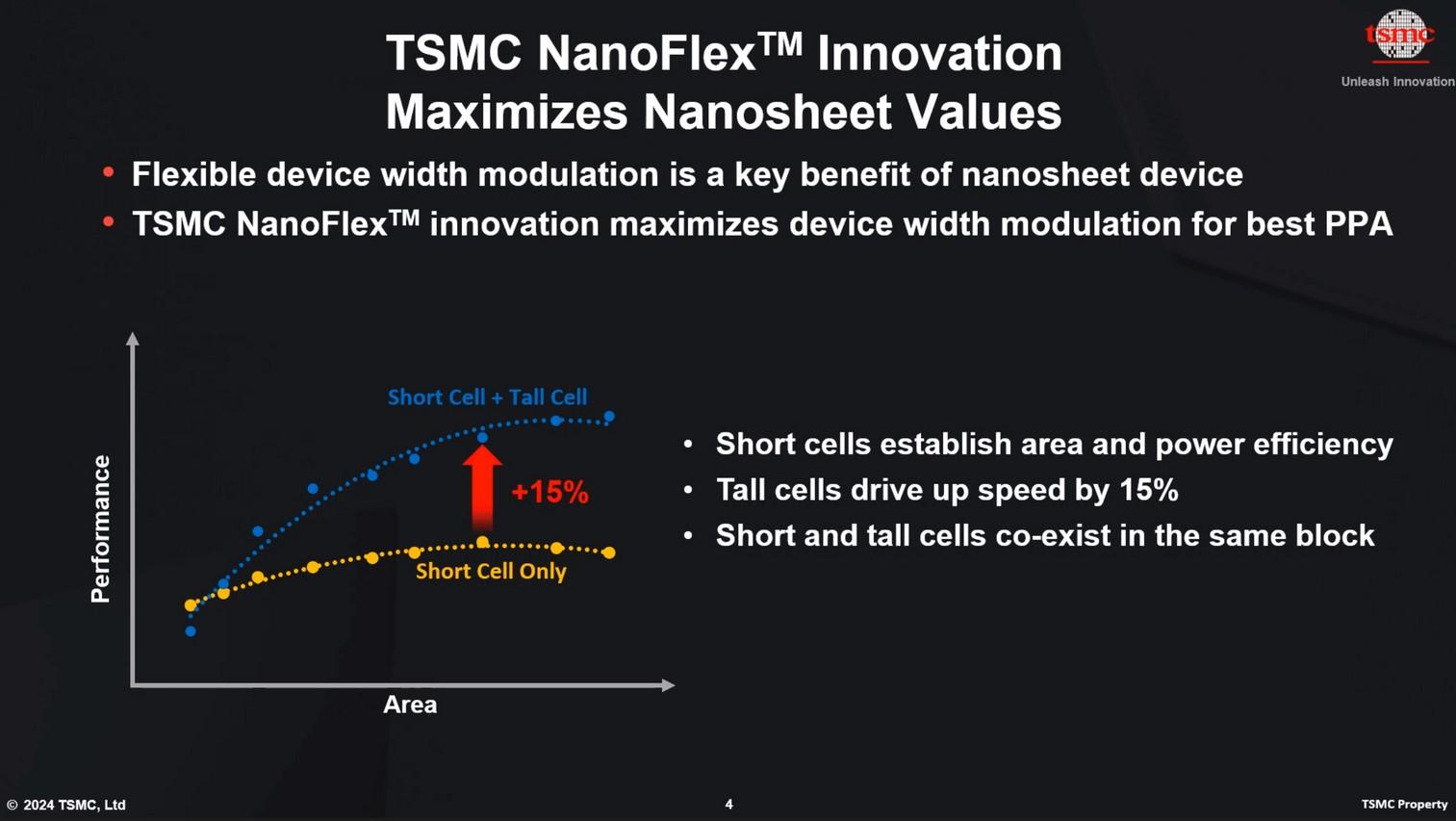

Pour en finir avec le 2 nm, le fondeur poussera la philosophie de son FinFlex plus loin avec NanoFlex. Cette approche donne une grande flexibilité aux concepteurs de puces en leur permettant de mélanger et d'associer des cellules standard de différentes bibliothèques au sein d'un même bloc.

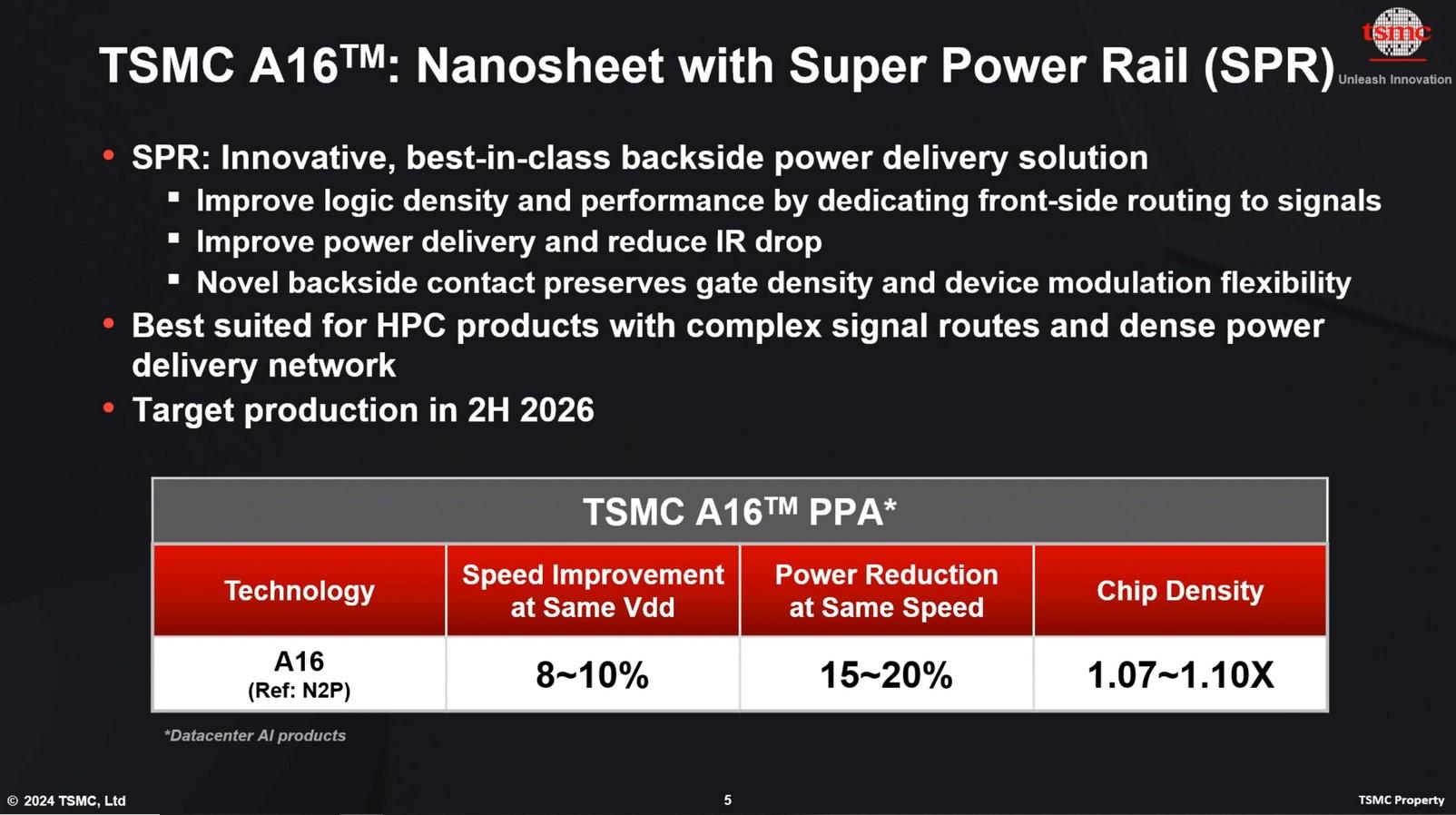

Après le 2 nm viendra l’A16. Contrairement à Intel, qui parle d’angström dès le 20A, TSMC emploie donc ce terme à partir du 1,6 nm. Vous l’aurez compris si vous avez lu ce qui précède, la principale innovation sera le réseau de distribution d'énergie par l'arrière. Le fondeur la nomme SPR, pour Super Power Rail. Comme stipulé dans l'une des diapositives, cette technologie doit répondre aux besoins des processeurs IA et HPC, ces derniers ayant tendance à avoir un câblage de signaux complexe et des réseaux de distribution d'énergie denses. Les transistors seront toujours de type GAA.

Précisons qu’Intel proposera aussi du backside power delivery d'ici quelques mois. L'entreprise appelle sa techno PowerVia. Elle sera active à partir du 20A.

Dans les grandes lignes, l'emploi d'un rail d'alimentation arrière vise à séparer le câblage d'alimentation et d'E/S. Pour mettre cette BSPN (backside power delivery network technology) en œuvre, il y a pour le moment trois grandes méthodes. Outre les deux susmentionnées, la dernière est le Buried Power Rail d'Imec. Elle s'appuie sur des rails d'alimentation enterrés tandis que le PowerVia a recours à des Nano TSV pour acheminer l'énergie jusqu'à la couche de transistors (d'où son nom).

TSMC présente son Super Power Rail comme un réseau d'alimentation arrière directement relié à la source et au drain de chaque transistor. Le fondeur présente logiquement sa technologie comme la plus efficace. Sa complexité aurait toutefois des répercussion sur les coûts de production.

C’est sans doute la raison pour laquelle TSMC n’ a pas recours au SPR dès le N2. Le fondeur souhaite à l’évidence proposer du 1,6 nm avec des transistors GAA / SPR et de l’autre côté, du 2 nm uniquement GAAFET. A priori, ces deux nœuds ne se feront pas directement concurrence et offriront des avantages distincts pour répondre aux demandes des différents clients.

Par rapport au N2P, le 16A promet une fréquence d'horloge jusqu'à 10 % plus élevée à la même tension et une consommation d'énergie de 15 à 20 % inférieure à la même fréquence et à la même complexité. En outre, la nouvelle technologie pourrait permettre d'augmenter la densité des transistors de 7 à 10 %, en fonction de la conception réelle.

Sur la feuille de route, l’A16 est à cheval entre la toute fin de 2026 et 2027. Au passage, notez que Kevin Zhang, vice-président du développement commercial chez TSMC, a déclaré à Reuters que l’A16 ne nécessitait pas d'outils de lithographie EUV de nouvelle génération – autrement dit, des scanners EUV High-NA d'ASML, dont le premier exemplaire a récemment été inauguré par Intel.

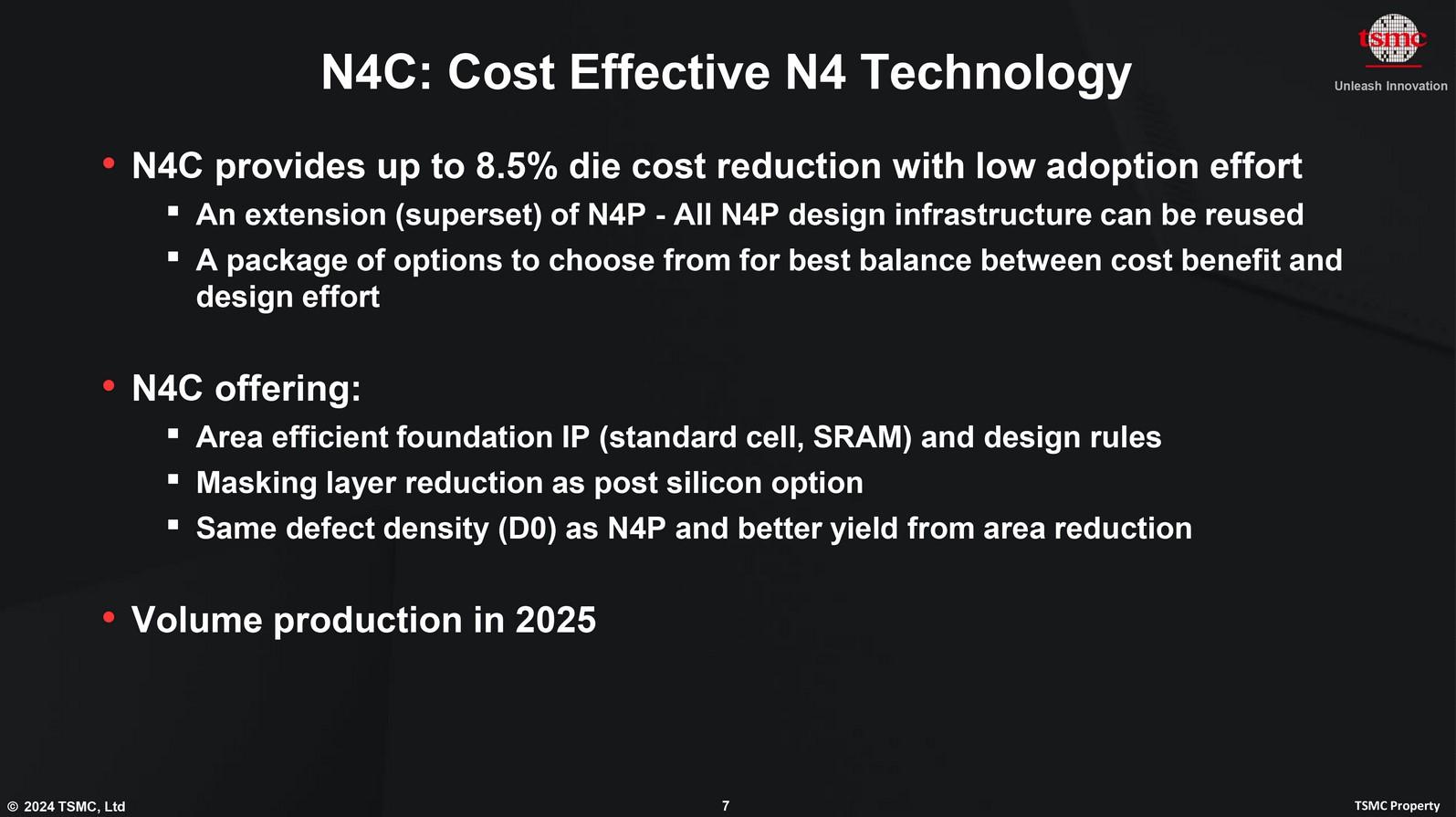

Terminons en revenant à des nœuds un peu plus actuels. TSMC a étoffé sa famille 4 nm avec le N4C. C’est essentiellement un processus de fabrication bon marché qui apporte quelques optimisations.

Kevin Zhang, vice-président du développement commercial chez TSMC, a expliqué :

« Nous n'en avons donc pas fini avec nos [technologies] 5 nm et 4 nm. Entre le N5 et le N4, nous avons amélioré de 4 % la densité du rétrécissement optique et nous continuons à améliorer les performances des transistors. Aujourd'hui, nous ajoutons la technologie N4C à notre portefeuille de technologies 4 nm. La technologie N4C permet à nos clients de réduire leurs coûts en supprimant certains masques et d'améliorer la conception originale de la propriété intellectuelle, comme une cellule standard et une SRAM, afin de réduire davantage le coût global du produit ».

Dans le communiqué de presse de TSMC, le fondeur présente le N4C comme « une extension de la technologie N4P avec une réduction de 8,5 % du coût du die ». La société ajoute qu'il ne nécessite pas de grands changements en matière de conception, puisque le N4C s’appuie sur « une IP de base et des règles de conception qui sont entièrement compatibles avec la technologie N4P largement adoptée ». La production en volume débutera en 2025.

| Un poil avant ?Instabilités des Core Raptor Lake : Intel nie toute responsabilité | Un peu plus tard ...La console portable MSI Claw baisse sa facture et gonfle ses performances |  |