SK Hynix « détaille » sa vision de la NAND et de la DRAM du futur |

————— 24 Mars 2021 à 10h46 —— 15371 vues

SK Hynix « détaille » sa vision de la NAND et de la DRAM du futur |

————— 24 Mars 2021 à 10h46 —— 15371 vues

Lors de l'International Reliability Physics Symposium de l'IEEE, SK Hynix, représenté par son PDG et une poignée d'autres cadres haut placés, a abordé certains des objectifs technologiques de l'entreprise à plus ou moins long terme, une sorte de feuille de route conceptuelle basée sur le meilleur des scénarios et une vision pour le moins relativement optimiste.

Grâce à son évolutivité et son efficacité architecture, SK Hynix ne voit pas la NAND 3D nous quitter de sitôt, bien au contraire. Certes, sous condition de la réalisation des bonnes innovations, de l'amélioration des matériaux et de la conception de manière générale, tout en arrivant à résoudre les problèmes de fiabilité à chaque étape, le producteur coréen imagine qu'il sera à l'avenir parfaitement possible d'atteindre les 600 couches de NAND (rappelons que SK Hynix en est à 176 depuis décembre dernier, à peu près comme la plupart des autres acteurs).

Ce n'est pas la première fois que les dirigeants de la boite mentionnent de tels chiffres, il y a quelques années le constructeur parlait déjà d'une NAND 3D 500 couches. Clairement, la confiance est toujours de mise quant à la capacité de la technologie d'aller encore bien au-delà. Une telle densité sous-entend des couches toujours plus fines et des cellules toujours plus petites, et nécessitera de nouveaux matériaux et techniques de fabrication, comme l'empilement de wafers. En attendant, ne demandez pas quand cela pourrait se faire, personne ne se risque encore d'avancer des projections datées.

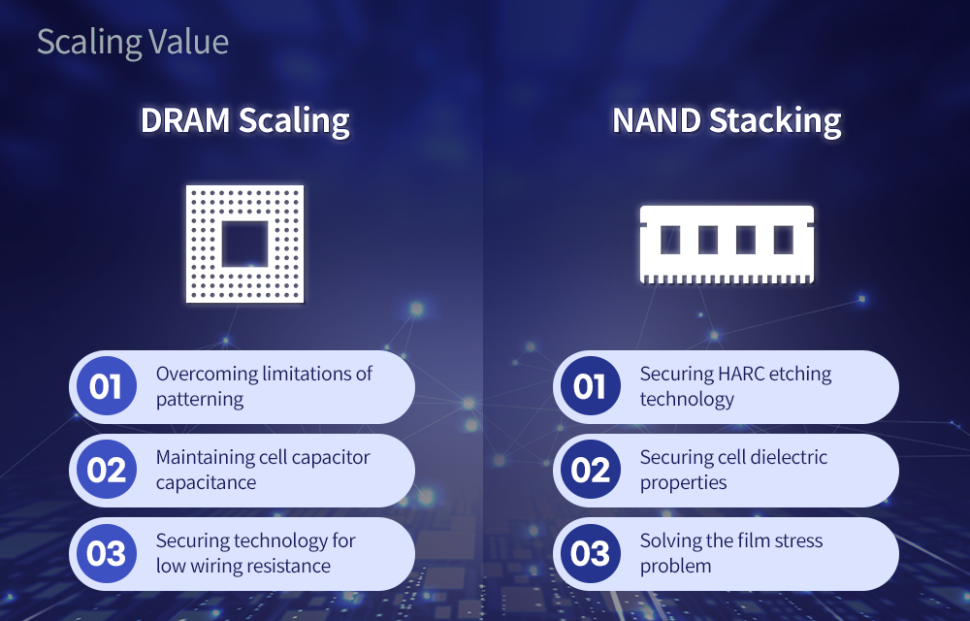

Bien entendu, ce qui se fera du côté NAND servira aussi pour la DRAM, notamment en ce qui concerne l'évolution des matériaux, des techniques de fabrication et de la conception. On le sait déjà, pour la DRAM sous la barre des 10 nm, c'est l'EUV qui tiendra une place très importante dans la poursuite de capacités et de performances toujours plus élevées, tout en arrivant à maintenir des niveaux de consommation corrects. Les choses sont ici beaucoup moins théoriques qu'avec l'idée d'une NAND 600L, puisque Samsung aussi est sur le coup de l'adoption d'une lithographie EUV pour la nouvelle génération de DRAM « 1a », tandis que Micron a décidé d'y faire l'impasse pour le moment. L'implémentation de l'EUV passera par le développement de nouveaux matériaux et de résine photosensible pour une structuration stable et une bonne gestion des défauts. SK Hynix cherche également à trouver un moyen pour réduire la résistance du métal d'interconnexion, afin de pallier le fait que les transistors de sa DRAM devenus tellement petits risquent de devenir des goulots d'étranglement à partir de 10 nm. SK Hynix n'a pas dit s'il compte utiliser du cobalt comme Intel ou un processus de dépôt sélectif de tungstène comme Samsung et TSMC, mais il y travaille.

Enfin, SK Hynix aussi voit un avenir pour la convergence de la mémoire DRAM et du dispositif logique, où l'un et l'autre existent au sein d'un même die, ce que le constructeur qualifie de Processing In Memory (PIM) - faisant écho à ce que Samsung a fait avec sa nouvelle mémoire HBM2 annoncée le mois dernier (HBM-PIM), intégrant 32 unités programmables fonctionnant à 300 MHz et capable de réaliser du calcul FP16. Cette dernière devrait par ailleurs devenir un standard du JEDEC. La compagnie n'en a pas dit beaucoup plus, mais on peut imaginer que ce type d'intégration poussée pourra beaucoup bénéficier à certains types d'usage assez courant. En tout cas, l'industrie de la mémoire semble donc partager une vision assez similaire de la mémoire de demain. (Source)

![La magie de la loupe, sans loupe sk hynix [cliquer pour agrandir]](/images/stories/_business/sk-hynix-ere-de-la-convergence-memoire-cpu_t.png)