DDR6 et LPDDR6 : les nouvelles générations accélèrent le rythme |

————— 23 Mai 2024 à 19h37 —— 27050 vues

DDR6 et LPDDR6 : les nouvelles générations accélèrent le rythme |

————— 23 Mai 2024 à 19h37 —— 27050 vues

Tandis que la forte demande en HBM est fatale à la DDR3 chez certains fabricants, beaucoup de systèmes exploitent actuellement la DDR4. La transition avec la DDR5 a factuellement commencé en 2021 mais prend du temps, bien que l'AM5 ait été la première plateforme exclusivement compatible DDR5. Vous vous en doutez, les fabricants esquissent déjà leurs plans pour la suite, à savoir la DDR6 (ainsi que la LPPDR6). Des données en provenance de Synopsys ont récemment été publiées.

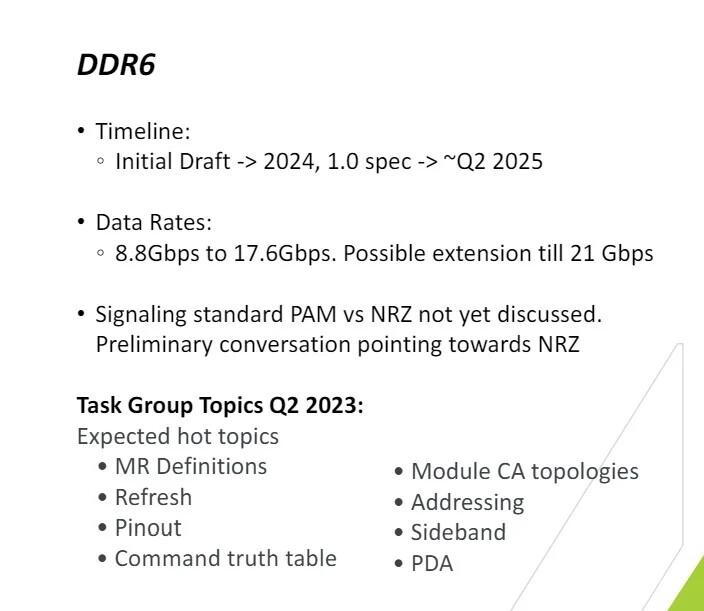

Selon l’une des diapositives, les taux de transfert de données de la DDR6 devraient commencer à 8,8 Gbit/s et aller jusqu'à 17,6 Gbit/s. Le document n’écarte pas la possibilité de monter à 21 Gbit/s. Autrement dit, nous parlons là de DDR6-8800 et de DDR6-17600, voire de DDR6-21333. Ce dernier chiffre est assez révélateur puisqu’il est dix fois supérieur à la DDR4-2133, la vitesse initiale de la DDR4, un type de mémoire lancé en 2014, soit il y a dix ans.

Rappelons que Synopsys est un membre du JEDEC. En principe, l’organisme devrait commencer à spécifier la DDR6 dans le courant de l’année et publier les caractéristiques finales à la mi-2025.

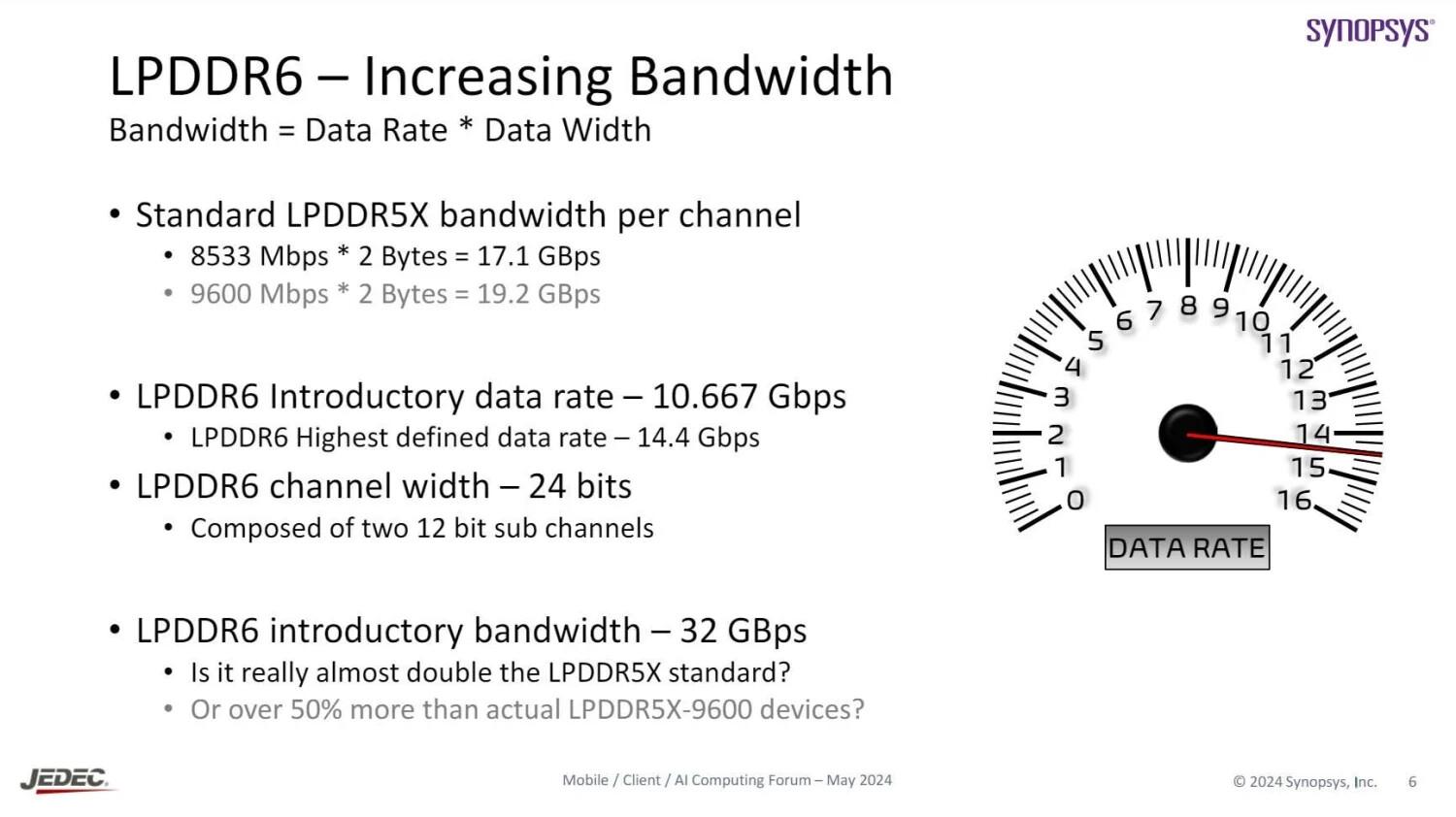

Les documents mentionnent aussi la LPDDR6, la mémoire à faible consommation d’énergie. Contrairement à la DDR5, la LPPDR5, est désormais bien ancrée dans nos appareils. Selon la fuite du jour, la LPDDR6 proposera un débit standard de 10,667 Gbit/s (LPDDR6-10667) sur un canal de mémoire de 24 bits avec deux sous-canaux de 12 bits. Le débit maximal pour la LPDDR6 sera de 14,4 Gbit/S (LPDDR6-14400).

Le JEDEC prévoit de publier la version 1.0 de la LPPDR6 au cours du troisième trimestre de cette année. Le déploiement de cette mémoire débutera sans doute en 2025 dans quelques dispositifs.

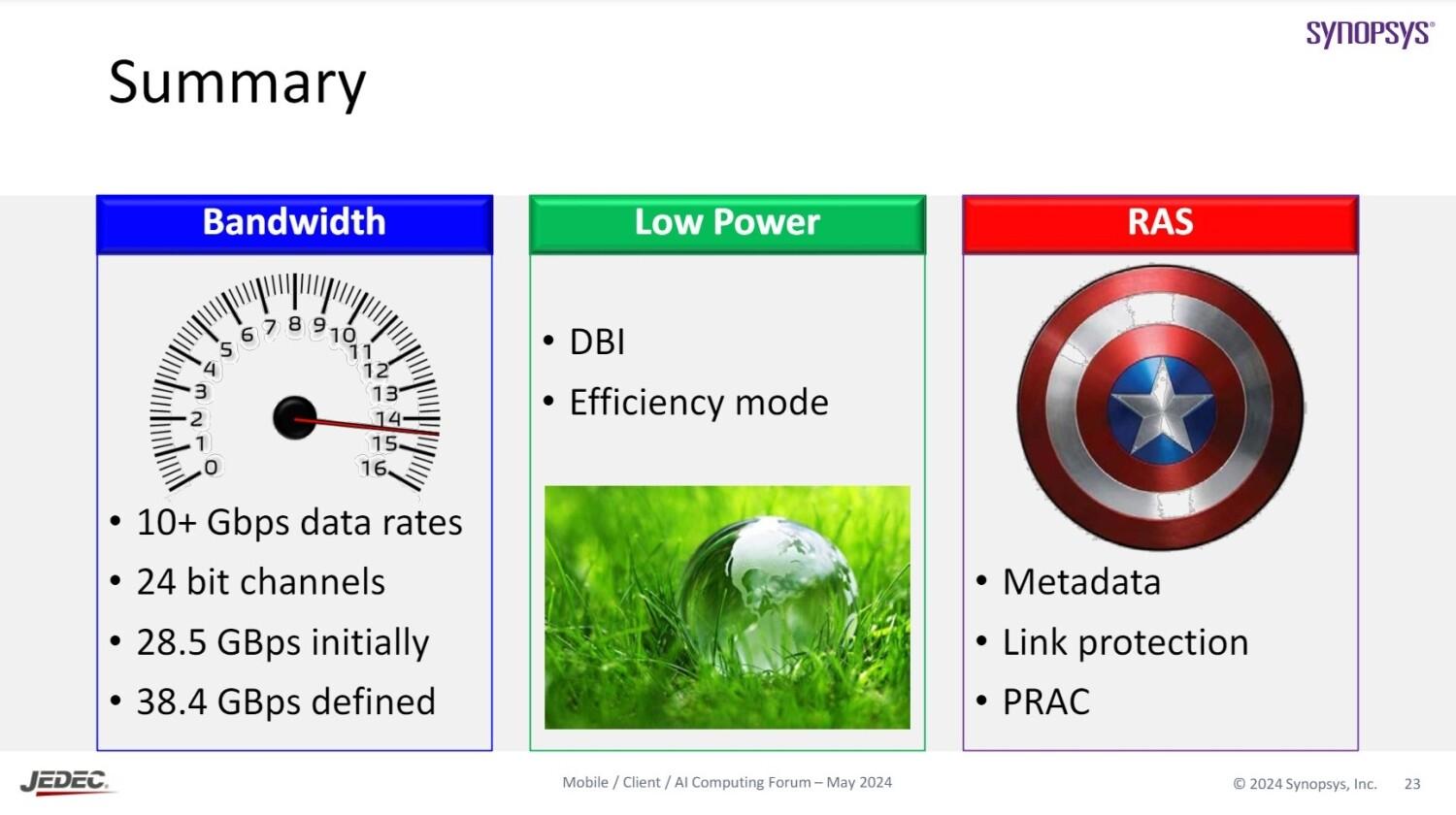

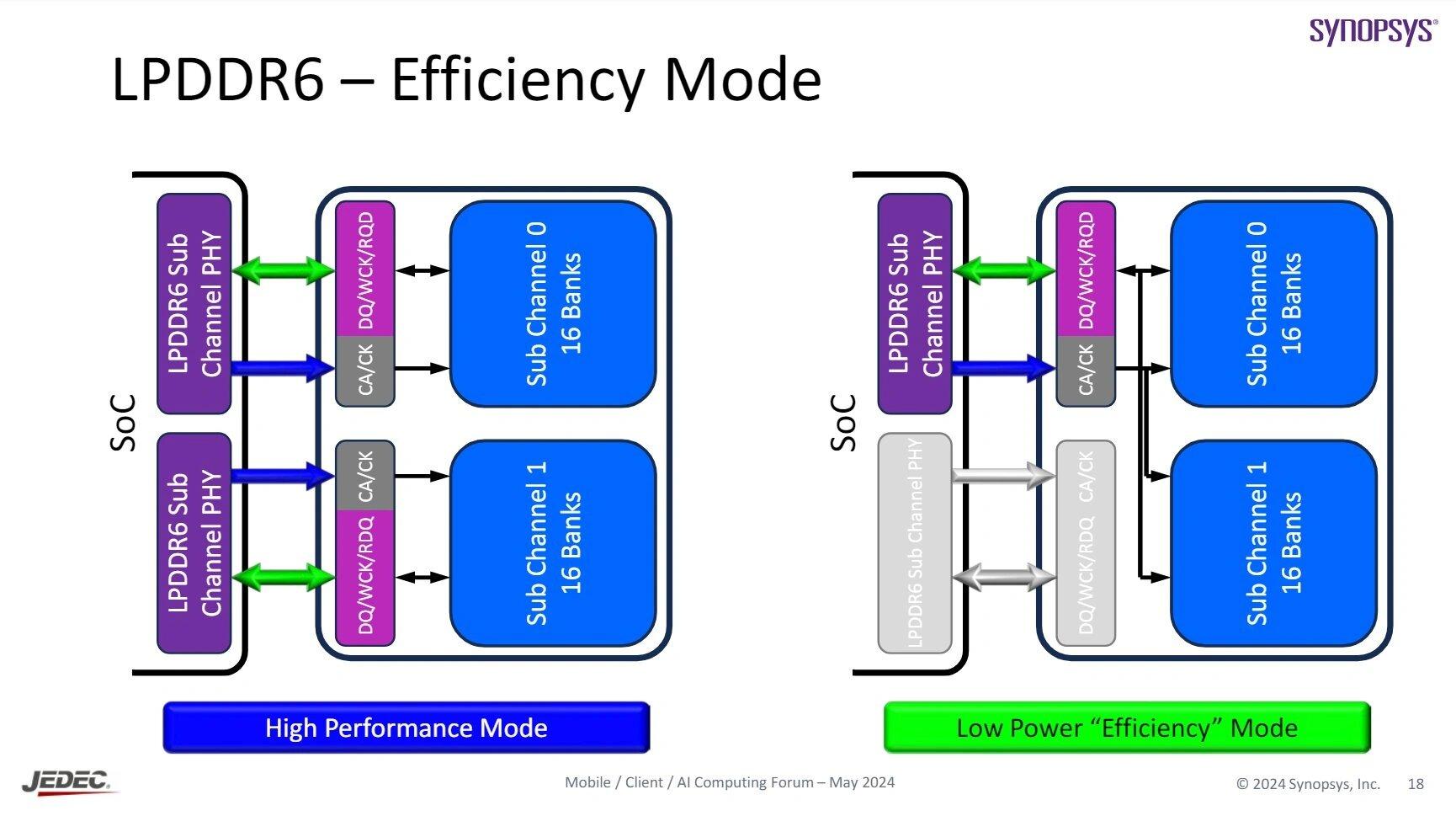

Outre ces augmentations générationnelles de la bande passante, les mémoires DDR6 et LPDDR6 introduiront vraisemblablement plusieurs fonctions de sécurité et d'efficacité énergétique. Pour le second aspect par exemple, des diapositives détaillent notamment un « mode d'efficacité » conçu pour réduire la consommation d'énergie en mode veille.

Vous pouvez consulter les 15 pages de présentation via les publications du compte Darkmont sur le réseau social X.

— Darkmont (@DarkmontTech) May 21, 2024

| Un poil avant ?Après 8 années de service et 48 millions de tests, Time Spy fait son bilan | Un peu plus tard ...L’avènement des PC IA, une aubaine pour NVIDIA ? |  |