Samsung sur la route des NAND à 300+ couches... Et aussi sur celles à 400+ couches |

————— 21 Août 2023 à 18h01 —— 35543 vues

Samsung sur la route des NAND à 300+ couches... Et aussi sur celles à 400+ couches |

————— 21 Août 2023 à 18h01 —— 35543 vues

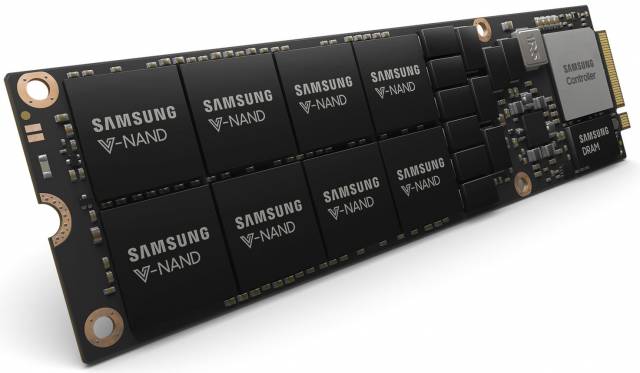

Bien le bonjour, après quelques soucis de DNSSEC depuis jeudi dernier, le Comptoir revient peu à peu des tréfonds du oueb. Pour fêter dignement ce retour placé sous un signe des plus caliente actuellement sur l'hexagone, direction la Corée, car la Corée c'est chez Sam et pas l'oncle, ou inversement. Faisant écho à SK Hynix qui kiffe le 421, et selon Digitimes via le Seoul Economic Daily , Samsung aurait calé sa production de V-NAND de 9e génération à plus de 300 couches empilées d'ici 2024, faisant le deuxième fabricant majeur de NAND à franchir le cap, alors que la production actuelle est basée sur de la NAND 236-l.

Du côté des specs techniques, rien à se coller sous la dent alors que le process doit être largement avancé, si ce n'est qu'à priori et contrairement à SK Hynix il y aura 2 piles contre trois pour ce dernier, soit à minima 150 couches par piles : on peut donc estimer que Samsung maitrise suffisamment sa chaine de production pour sortir des yields aux rendements satisfaisants, ou alors qu'ils profitent d'une baisse de production — une des meilleures cartes face aux baisses de demandes du marché, souvent utilisée — opérée depuis avril dernier pour conduire des tests en vue des NAND de demain et surtout d'après demain, puisque pas moins de 1000 couches sont visées à l'horizon 2030. Un peu moins loin, ce sont ~430 couches via 3 empilements qui devraient être de mise sur la 10e génération de la V-NAND sud-coréenne.

L'occasion de faire une rapide minute technique ! Ainsi, ces sandwichs de piles sont rendus plus faciles — tout est relatif — grâce à l'usage du TSV (Through-Silicon Vias), similaires aux interconnects en cuivre (comme ceux que vous pouvez facilement voir sur les PCB), mais destinés aux empilements verticaux. Ces voies métalliques à travers le silicium traversent littéralement ce dernier permettent non seulement de faire communiquer des puces différentes sur un plan vertical et donc une économie de place occupée notable (coucou la HBM), mais en plus de le faire avec plus de canaux d'échanges, donc de bande passante. Pour vous imaginer, ces vias ont des diamètres qui varient de 5 à plusieurs dizaines de microns. Sortez les lunettes ...

![Même pas cap' de cliquer coupe d'un TSV [cliquer pour agrandir]](/images/stories/_divers/tsv_t.png) Céfichukomen un TSV ? Bah comme ça. (source © HAL open science)

Céfichukomen un TSV ? Bah comme ça. (source © HAL open science)