Samsung lance le premier dispositif hybride CXL qui combine mémoire flash et DRAM |

————— 03 Avril 2024 à 16h59 —— 36638 vues

Samsung lance le premier dispositif hybride CXL qui combine mémoire flash et DRAM |

————— 03 Avril 2024 à 16h59 —— 36638 vues

Il y a quelques jours, dans le cadre de la Memcon 2024, Samsung a dévoilé de nouvelles solutions Compute Express Link (CXL) : la CMM-B, pour CXL Memory Module – Box ; la CMM-D pour CXL Memory Module - DRAM ; et surtout la CMM-H TM, pour CXL Memory Module-Hybrid for Tiered Memory, présentée comme une carte d’extension basée sur un FPGA (Field Programmable Gate Arrays) qui combine DRAM et NAND. L’entreprise coréenne l’a conçue en partenariat avec Vmware by Broadcomm.

Pas de veste en cuir à la Jensen Huang pour Jin-Hyeok Choi, qui tient un CMM-H dans la main © Samsung

Avant tout, rappelons que le CXL est une norme industrielle ouverte, lancée en 2019, qui fait office d’interconnexion ; nous pouvons la résumer à une sorte d’interface PCIe améliorée. Elle en est à sa troisième révision actuellement (basée sur le PCIe 6.0). N’hésitez pas à consulter notre précédent article sur le sujet pour plus de détails. Pour le moment, le CXL se limite aux centres de données, mais en 2022, AMD estimait que cette norme s’inviterait dans les PC domestiques d’ici 3 à 5 ans, soit entre 2025 et 2027.

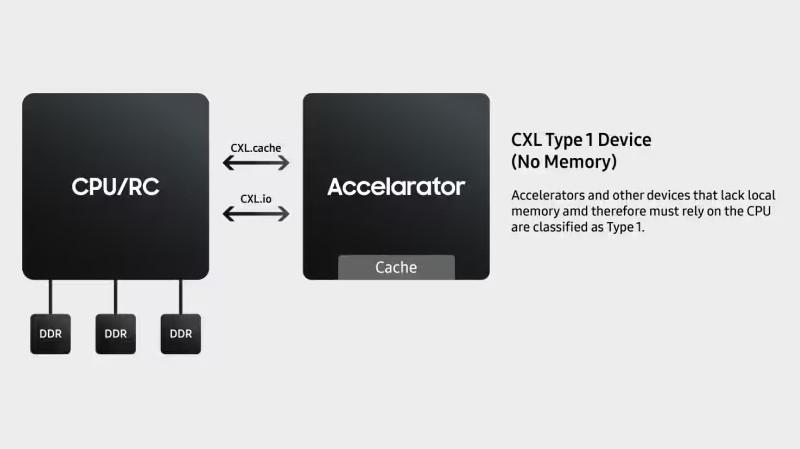

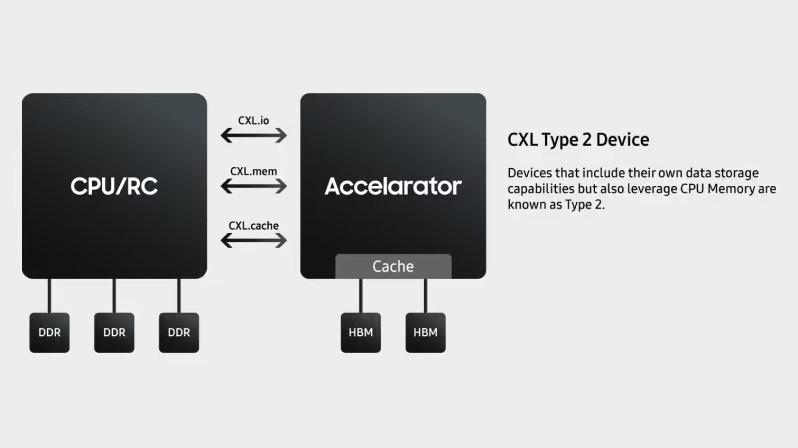

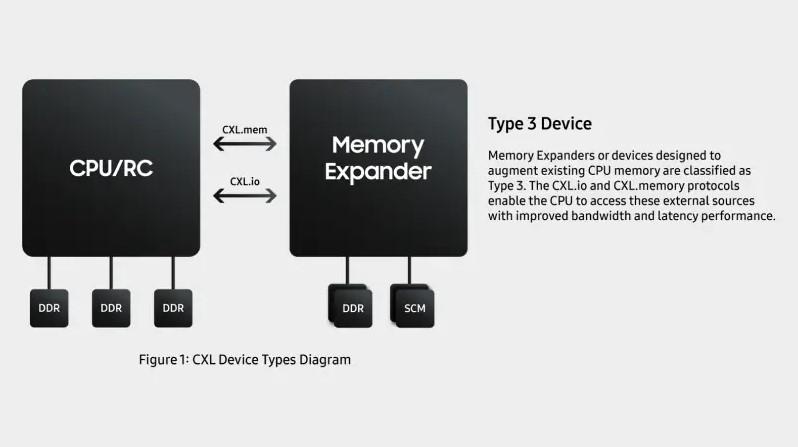

La spécification CXL prend en charge trois types de dispositifs. Comme le rappelle Samsung, le Type 1 est utilisé dans les dispositifs de mise en cache tels que les accélérateurs et les SmartNIC. Le Type 2 concerne les GPU et les FPGA qui ont des mémoires telles que DDR et HBM attachées au dispositif. Le Type 3 concerne les dispositifs d'extension de mémoire qui permettent aux processeurs hôtes d'accéder au cache de mémoire du dispositif CXL de manière cohérente par le biais de transactions cxl.mem.

La CMM-H TM est de Type 3. Samsung affirme qu'il s'agit de la première solution de mémoire hiérarchisée au monde basée sur un FPGA. L’entreprise la présente comme « une solution hybride qui combine des supports DRAM et NAND dans un format de carte d'extension (AIC) ». Elle doit permettre de répondre aux « enjeux de la gestion de la mémoire, réduire les temps d'arrêt, optimiser la planification de la mémoire hiérarchisée et maximiser les performances, tout en réduisant de manière significative le coût total de possession (TCO) ».

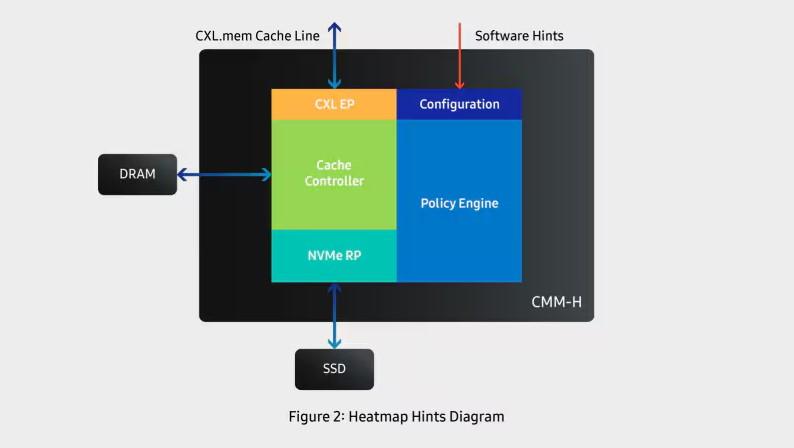

CMM-H © Samsung

Plus précisément, la société explique que la raison d'être du CMM-H est sa capacité à combiner de la mémoire flash NAND avec l'interface load/store CXL. Elle souligne que sa solution « propose de grands nœuds NUMA avec le cadre existant du noyau Linux et s'intègre de manière transparente dans les applications sans qu'il soit nécessaire de les modifier ». Samsung ajoute que « pour les applications qui privilégient la capacité, le coût total de possession et le débit par rapport à la latence de l'accès aléatoire, CMM-H est un excellent choix de conception » ; souligne que « la persistance des données intégrée permet de minimiser les temps d'arrêt lors de la récupération des données ».

© Samsung

Concrètement, la CMM-H n'est bien sûr pas aussi rapide que la DRAM, mais contrebalance une partie de sa latence via une une fonction de mise en cache. Les données chaudes sont déplacées vers les puces DRAM de la carte pour améliorer la vitesse, tandis que les données moins utilisées sont stockées dans la mémoire NAND. Ce processus s’effectue de manière automatique, mais il est également possible d’affiner ce comportement via des API.

En conclusion, Samsung stipule :

« Les solutions de modules de mémoire de Samsung ouvrent la voie à l'intelligence artificielle, à l'apprentissage automatique et au traitement des grands modèles de langage. La prise en charge d'une plus grande partie du traitement des données et son placement dans et autour des modules de mémoire redéfinissent la manière dont l'informatique sera effectuée dans cette nouvelle ère de l'IA. »

La CMM-B peut accueillir huit dispositifs CMM-D de format E3.S et fournir jusqu'à deux téraoctets de capacité. Samsung renseigne jusqu'à 60 Go/s de bande passante et un temps de latence de 596 nanosecondes.

CMM-B © Samsung

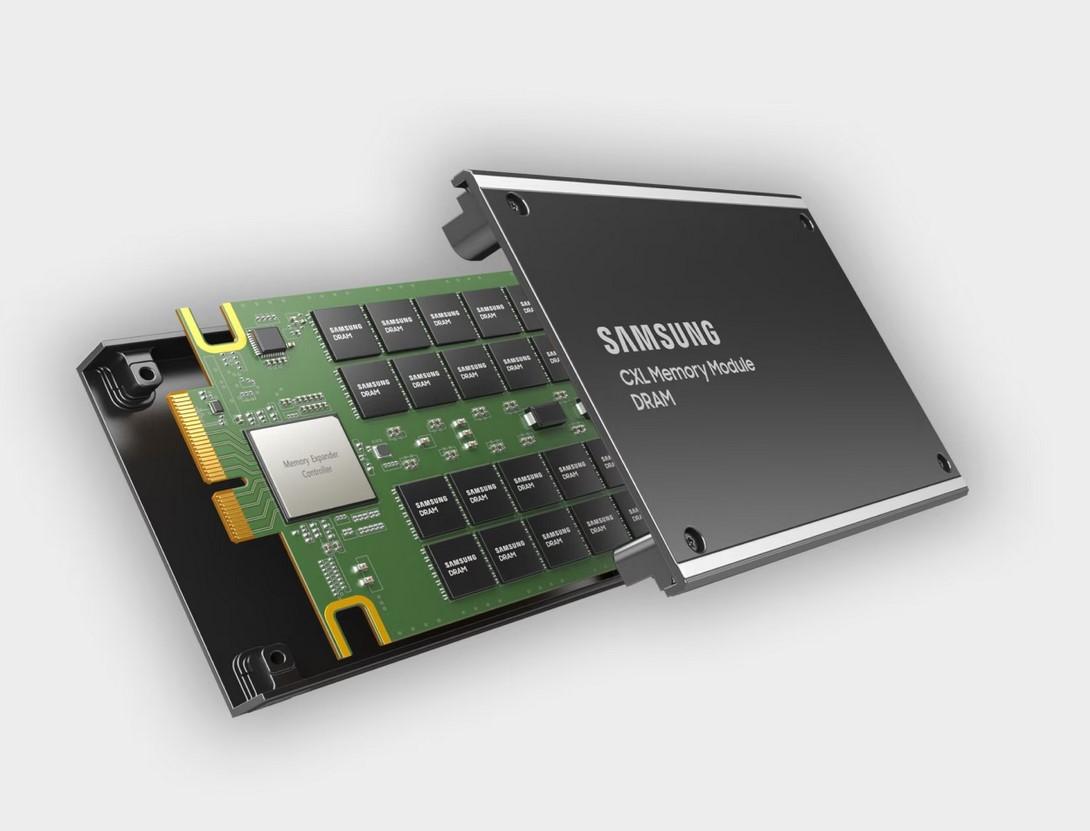

Enfin, la CMM-D et un module DRAM exploitant l'interface CXL. Ce dispositif vient d’être validé par Red Hat. Dans le cadre du Samsung Memory Research (SMRC), les deux entreprises s’emploient à développer des modèles de référence basés sur du code source ouvert CXL.

CMM-D © Samsung

Vous pouvez consulter le communiqué de Samsung pour obtenir davantage d'informations. Il contient des liens vers des pages détaillant chaque solution.