Ryzen AI Strix Halo : 4 nm intégral et interconnexion entre chiplets atypique |

————— 15 Janvier 2025 à 19h55 —— 29883 vues

Ryzen AI Strix Halo : 4 nm intégral et interconnexion entre chiplets atypique |

————— 15 Janvier 2025 à 19h55 —— 29883 vues

Les Ryzen AI Strix Halo nous intriguent depuis plusieurs mois ; ils sont officiels depuis le CES 2025. Et apparemment, ce ne sont pas « juste » de musculeux processeurs atrophiés de cœurs : leur flux sanguin inter-chiplets est assuré par un système d’interconnexion parallèle de type « sea of wires » plutôt que via une approche SerDes (serializer/deserializer) calquée sur celle des Ryzen 9000 desktop.

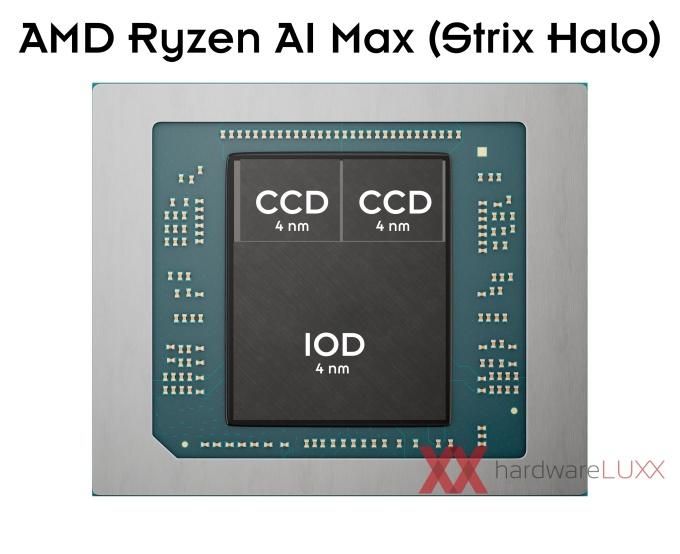

Du 4 nm partout © HardwareLuxx

C’est ce qui ressort d’une séquence proposée par la chaîne Chips and Cheese et relayée notamment par HardwareLuxx. La source nous apprend que les Ryzen AI Strix Halo exploitent logiquement deux Core Complex Dies (CCD). Ils sont élaborés sur le processus N4 (4 nm) de TSMC et comprennent jusqu'à huit cœurs Zen 5, comme ceux des Granite Ridge et des Ryzen précédents. Seulement pour les puces mobiles, le processus de gravure N4 sert également à l’IOD (I/O die) ; celui des Ryzen desktop Zen 5 est fabriquée en 6 nm (N6).

Ce n’est pas le seul changement ; un autre intervient dans les échanges entre les deux CCD et l’IOD. Alors que la série Ryzen 9000 utilise des PHY SerDes pour convertir les transmissions parallèles en transmissions sérielles, Strix Halo met en œuvre la transmission directe de données parallèles par le biais de plusieurs connexions physiques.

Sur le papier, le principe du SerDes est simple : il convertit les données parallèles en données série (la sérialisation), puis les reconvertit en données parallèles à l'arrivée (la désérialisation). Le but de la manœuvre est de réduire le nombre de connexions entre l'émetteur et le récepteur. Notre confrère de HardwareLuxx indique qu’un telle connexion permet une transmission efficace sur de plus longues distances, car les signaux sériels sont moins sensibles aux interférences et plus faciles à transmettre qu’en mode parallèle, et que cette transmission en série permet d'atteindre des débits de données plus élevés par ligne. En revanche, cette approche a un impact négatif sur la latence et la consommation d’énergie.

Pour Strix Halo, une connexion dite « sea of wires » transmet les données en parallèle via une multitude de lignes (les canaux qui transportent les données). Par apport au SerDes, les latences sont ainsi plus faibles, car les données sont transmises simultanément. Il n'y a pas de délais imputables à la sérialisation / désérialisation. En outre, la distance entre les puces est suffisamment courte pour ne pas souffrir d’interférences.

La contrepartie de cette accumulation de lignes parallèles : forcément davantage de place occupé sur le circuit imprimé, plus de broches pour la connexion externe, ce qui aboutit à une conception globalement plus complexe. En conséquence, il est probable qu’AMD ait dû procéder à de petites modifications des CCD.

Quoi qu’il en soit, ce changement d'approche aurait été « motivé par la nécessité de réduire la latence et la consommation d'énergie dans les charges de travail à forte intensité de données, où une communication constante à large bande passante entre les chiplets est cruciale ».

Il faudra patienter encore quelques semaines pour découvrir le résultat ; les Ryzen AI Max Series doivent faire leurs preuves avant la fin du semestre.

| Un poil avant ?Les Ryzen retrouve un Raphael, déclassé sous une tente de camping | Un peu plus tard ...Pas mal d’infos rassurantes pour les RX 9000 (MAJ) |  |