IBM présente Telum II |

————— 28 Août 2024 à 18h48 —— 23869 vues

IBM présente Telum II |

————— 28 Août 2024 à 18h48 —— 23869 vues

IBM a profité de la Hot Chips 2024 pour présenter sa deuxième génération de processeurs de la dynastie Telum, sobrement appelée Telum II. Bon, vous jouez peut-être dans la même cour que le loup de Wall Street, mais pour les louveteaux de la CAPFI (Champagne-Ardenne place financière) que nous sommes, cette puce ne nous concerne pas vraiment : elle exécute des algorithmes IA pour sécuriser les transactions bancaires du monde de la finance.

Mi-Loup, mi-Leo

Sorti en 2021, Telum I est gravé en 7 nm par Samsung et compte 22 milliards de transistors. Il possède huit cœurs cadencés à 5 GHZ, 32 Mo de cache L2 par cœur. Les caches de niveau 2 forment un cache virtuel de niveau 3 de 256 Mo et un cache virtuel de niveau 4 de 2 Go.

Telum II reste fabriqué par Samsung mais en 5 nm, pour un total de 43 milliards de transistors. Il y a toujours huit cœurs, mais cadencés à 5,5 GHz désormais. En outre, il intègre un DPU spécialisé dans l'accélération des entrées-sorties. Il y a dix caches de niveau 2 de 36 Mo : un pour chaque cœur, un pour le DPU, et un dernier pour l’ensemble de la puce. La mémoire virtuelle L3 et la mémoire virtuelle L4 passent respectivement à 360 Mo et à 2,88 Go, soit des hausses de 40 % par rapport à la précédente génération.

Telum II exploite aussi des accélérateurs d'IA améliorés qui offrent individuellement une puissance de calcul quatre fois supérieure à celle de leur prédécesseur, selon IBM. L’entreprise évoque 24 TOPS avec une précision INT8 (contre 6 TOPS pour le Telum I).

Telum II reprend le principe de fonctionnement en « tiroirs » des puces qui, une fois combinées, forment une mainframe IBM-Z. À ce propos, l’entreprise précise « qu’au-delà des améliorations de calcul brut apportées par Telum II, nous avons apporté des améliorations au niveau du système dans le tiroir du processeur. Ces améliorations permettent à chaque accélérateur d'IA d'accepter du travail de n'importe quel cœur dans le même tiroir afin d'améliorer l'équilibre de la charge entre les huit accélérateurs d'IA. Cela permet à chaque cœur d'accéder à une plus grande accélération IA à faible latence, conçue pour 192 TOPS disponibles lorsqu'ils sont entièrement configurés entre tous les accélérateurs IA du tiroir ».

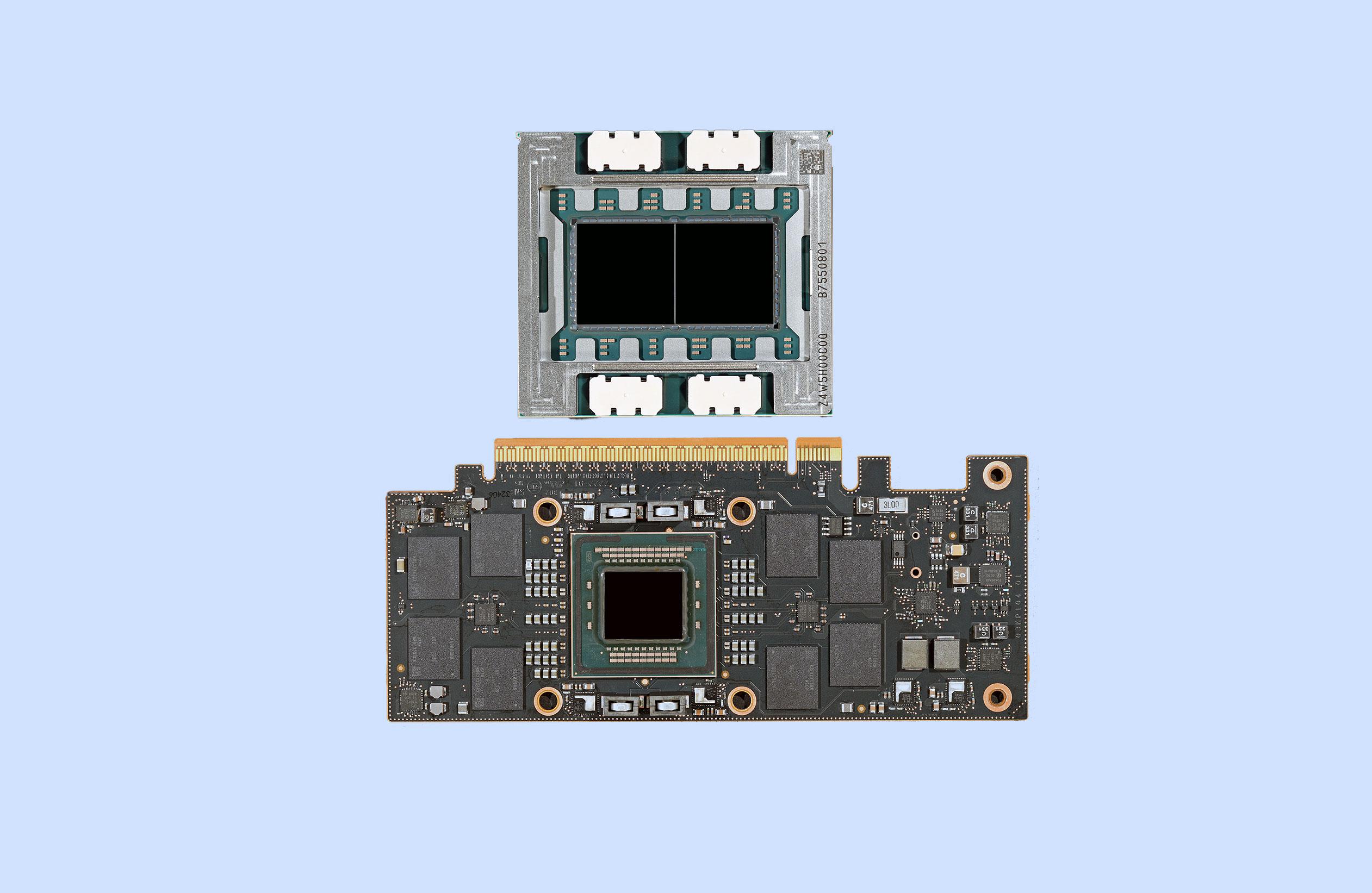

Telum II et Spyre AI © IBM

Outre Telum II, IBM a présenté ses accélérateurs Spyre AI. Ils renferment 32 cœurs d’IA et exploitent « une architecture similaire à l'accélérateur d'IA intégré dans la puce Telum II ». Plusieurs accélérateurs IBM Spyre peuvent être connectés au sous-système E/S d'IBM Z via PCIe afin d’augmenter la puissance de traitement. Spyre contient 26 milliards de transistors et est fabriqué sur le nœud de production 5LPE de Samsung.

Le processeur Telum II et l'accélérateur Spyre sont tous deux conçus pour prendre en charge ce qu'IBM appelle des méthodes d'IA d'ensemble, et qui impliquent l'utilisation de plusieurs modèles d'IA pour améliorer la précision et la performance des tâches. L’entreprise donne l’exemple de la détection des fraudes. IBM soutient que la combinaison de réseaux neuronaux traditionnels avec de grands modèles de langage améliore de manière significative la détection d'activités suspectes.

Le processeur Telum II et l'accélérateur Spyre seront disponibles en 2025. IBM n’a pas précisé quand. Consultez le communiqué de presse qui traite de ces deux produits sur le site d'IBM ; le document renvoie vers des fiches produits qui n'apportent pas d'autres informations pour le moment.